Key Benefits

- Boost engineering productivity up to 50%

- Single constraint environment at any stage of design

- Reduce respins and prototypes, speed time to market

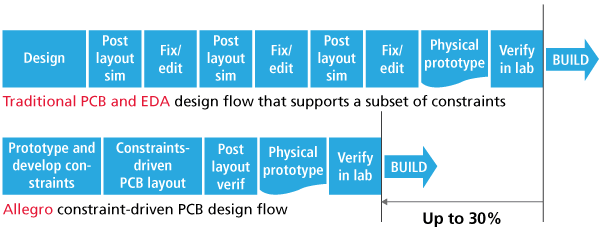

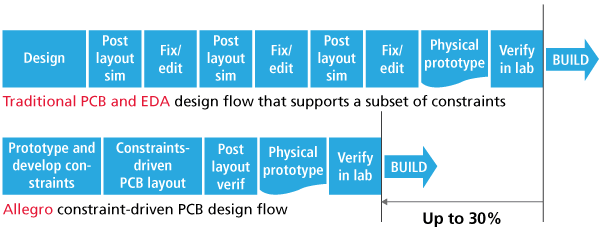

The Cadence® Allegro® constraint-driven design architecture provides a common, consistent constraint-management system for creation, management, and validation of constraints from front to back. It helps you eliminate unnecessary iterations and cut design cycles by up to four weeks.

Despite the shrinking size of today’s electronics products, there’s nothing small about the challenge of getting a product to market. These design pack more features and performance into less space. And at every point along the way, design issues are compounded and interrelated with complex ICs driving high-pin-count packages and multi-gigahertz boards.

The Allegro platform provides a unified flow that spans all three system domains. It begins with library management and continues through design entry, electrical constraint management, and powerful auto-interactive floorplanning and routing. The Allegro PCB design flow enables true collaboration and global constraint management, ensuring first-time design success. This constraint-driven approach also makes it very easy to enhance flows as your design needs grow.

Allegro Constraint-Driven Design Architecture

The Allegro constraint management system displays physical/spacing and high-speed rules along with their status in real time and is available at all stages of the design process. Each worksheet provides a spreadsheet interface that enables users to define, manage, and validate the different rules in a hierarchical fashion.

Route and Tune High-Speed Signals 4X Faster

See real-time delay and phase information right on the routing canvas. With the embedded route engine, the Allegro TimingVision environment provides real-time feedback during interactive editing and enhances your ability to develop a strategy for resolving timing on large buses or interfaces.

以下内容为机器自动翻译,可能存在翻译不准确的情况

约束驱动的设计架构为约束的创建、管理和验证提供了通用一致的系统,消除不必要的设计迭代,可缩短设计周期多达数周

主要好处

- 提高工程生产率高达50%

- 设计任何阶段的单一约束环境

- 减少旋转和原型,加快上市时间

Cadence® Allegro®约束驱动的设计架构为前后创建、管理和验证约束提供了一个通用、一致的约束管理系统。它帮助您消除不必要的迭代,并将设计周期缩短长达四周。

尽管当今电子产品的规模正在缩小,但将产品推向市场的挑战并不小。这些设计将更多的功能和性能打包到更少的空间中。在过程中的每一点,设计问题都是复杂的,并与驱动高针数软件包和多千兆赫板的复杂集成电路相关联。

Allegro平台提供了一个跨越所有三个系统域的统一流程。它从图书馆管理开始,并通过设计输入、电气约束管理以及强大的自动交互式平面图和路由继续。Allegro PCB设计流程支持真正的协作和全球约束管理,确保首次设计成功。这种约束驱动的方法也使随着设计需求的增长而轻松增强流量。

Allegro约束驱动设计架构

Allegro约束管理系统实时显示物理/间距和高速规则及其状态,并在设计过程的所有阶段可用。每个工作表都提供了一个电子表格界面,使用户能够以分层的方式定义、管理和验证不同的规则。

路由和调谐高速信号的速度快4倍

直接在路由画布上查看实时延迟和相位信息。借助嵌入式路由引擎,Allegro TimeingVision环境在交互式编辑期间提供实时反馈,并增强您制定解决大型总线或接口计时策略的能力。