加快 PCB 原理设计和实现的层次化方法

Key Benefits

- 将原理设计和实现速度提高 15%

- 以更高的抽象水平设计 PCB

- 更快地针对基于标准的接口进行布线,包括 DDR3、DDR4、SATA 和 PCIe

系统设计师可能会采用 DDRx 和 PCI Express® (PCIe®) 等协议,以支持产品的性能、功耗和带宽需求。为了跟上设计周期的需求,您的原理设计和布局工具是否能够提供所需的速度和易用性?您可以运用一种层次化的接口感知方法,加速 PCB 原理设计和实现过程,并提高设计质量、性能和可靠性。

现在,您可以使用 Cadence® Allegro® PCB 设计流程,最新版本 (16.65) 新增了接口感知设计功能。最终,可以将原理设计和实现速度提高 15%。该功能使您可以在更高的抽象水平上设计 PCB,从而可以更快地针对基于标准的接口进行布线,包括 DDR3、DDR4、串行 ATA (SATA) 和 PCIe。

支持当今的高速接口

我们来看一下接口感知设计功能的工作原理。传统的原理设计工具会使用总线或捆绑,以及一组信号的单级层次化定义。但是,无法在单级层次结构中对当今的接口建模。要解决的其他挑战包括:约束数量增加、设计密度增加、引脚间距减小、多引脚系统数量增加以及布线设计的用时增加(面临着设计周期收紧和资源受限)。

为了快速、轻松地连接接口,Allegro PCB 设计流程中的层次化接口感知设计功能可以带来的优势包括:

- 在更高的抽象水平上进行原理设计,以提高效率

- 将接口定义传递给布局设计人员

- 指导关键部件的摆放并进行布线规划

- 允许您使用自动交互技术来进一步加速接口的分线、布线和调整

借助集成的功能,Allegro Design Entry HDL 中的 PCB 原理图设计技术可以在原理图中使用新的图形对象,从而实例化接口和层次化网络组,配置并将接口连接到部件和区块,并将接口应用于部件。

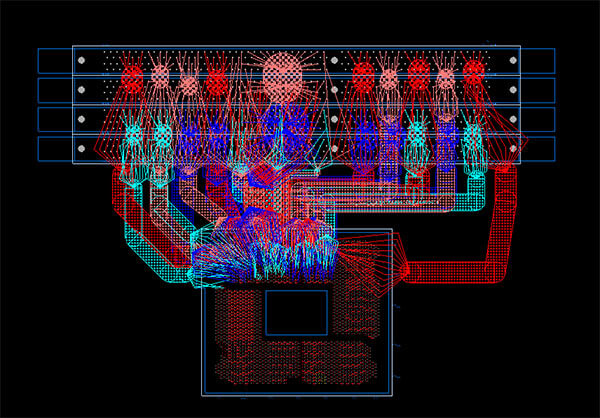

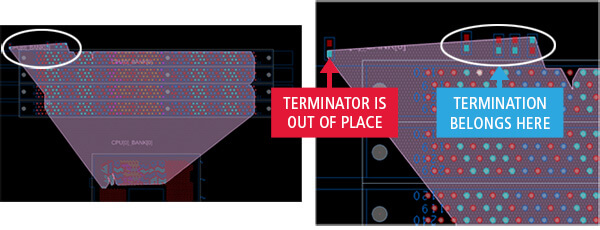

该功能支持多个层次化结构,因此可以更加轻松地将约束应用于以逻辑方式分组的信号。具有接口感知功能的 Allegro 工具(Allegro Design Authoring、Allegro Constraint Manager 和 Allegro PCB Editor)可在设计画布上自动创建并以可视化的形式标识网络组。这些工具还可以“嵌套”网络组,以纳入包含字节通道的子组。您能够查看接口的整个物理域,并找到未放置妥当的元件。通过网络组的颜色编码功能,可以轻松发现有问题的区域并应用适当的层分布。

总结

凭借 Allegro PCB 设计流程中可用的层次化接口感知设计能力,对高速接口(例如 DDRx 和 PCIe)进行布线将变得更快、更直接。该功能支持更高抽象级别的 PCB 设计,在提供视觉布局标示的同时加快了原理设计和实现的速度,并使您能够在设计周期的早期识别出布线问题。