Key Benefits

- Innovative environment with smart target technology

- Accelerates timing closure by 4X

- Solves timing closure challenge

Cadence® Allegro® TimingVision™ technology provides an innovative and unique environment that allows you to see real-time delay and phase information right on the routing canvas.

As data rates increase and supply voltages decrease in today’s high-performance interfaces (i.e. DDR3/DDR4, PCle® Gen3 and SATA), PCB and IC package designers have to spend more time to ensure that signals in an interface meet timing requirements. With increasing density, the effort to get to timing closure—ensuring all signals meet timing requirements—can increase significantly. Layout designers need new tools to meet this increasingly complex challenge.

With the embedded route engine, the Allegro TimingVision environment provides real-time feedback during interactive editing and enhances your ability to develop a strategy for resolving timing on large buses or interfaces such as DDRx and PCIe. Coupled with Auto-interactive Phase Tuning (AiPT) and Auto-interactive Delay Tuning (AiDT) capabilities, this environment lets you speed timing closure of high-speed PCB interfaces by up to 75%.

AiDT

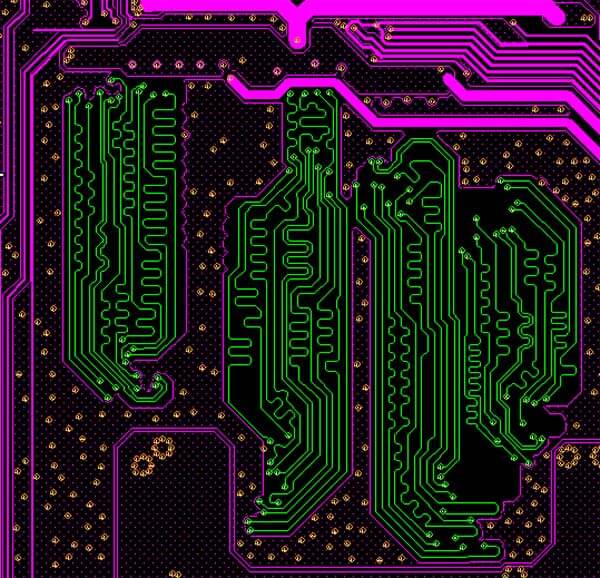

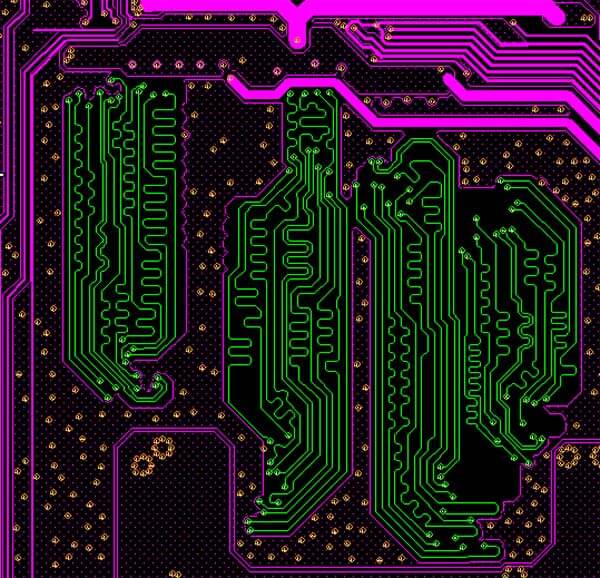

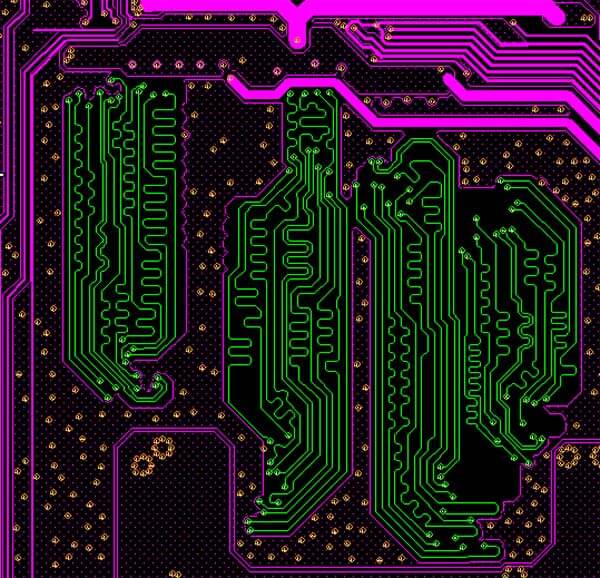

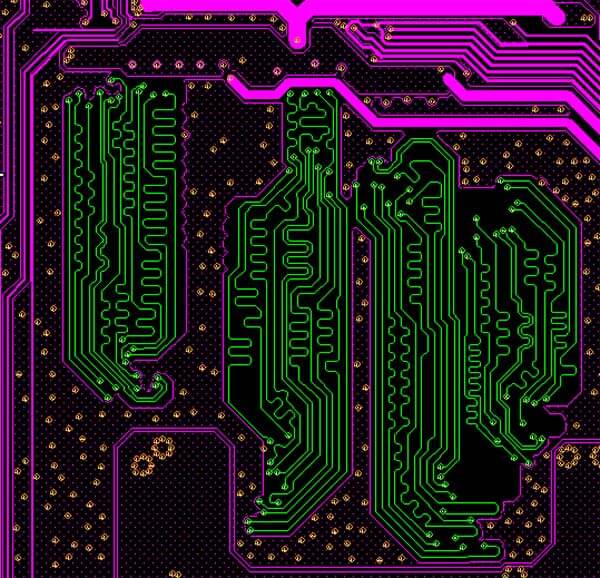

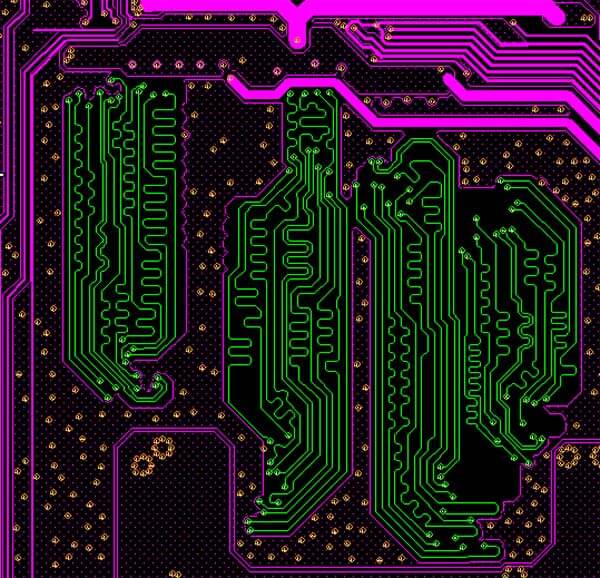

Auto-interactive Delay Tuning (AiDT) automatically generates tuning patterns on a user-selected routed byte lane or interface based on user-defined timing constraints and tuning parameters. AiDT computes the required length for the connections to meet timing constraints, and utilizes controlled push/shove techniques when adding tuning patterns.

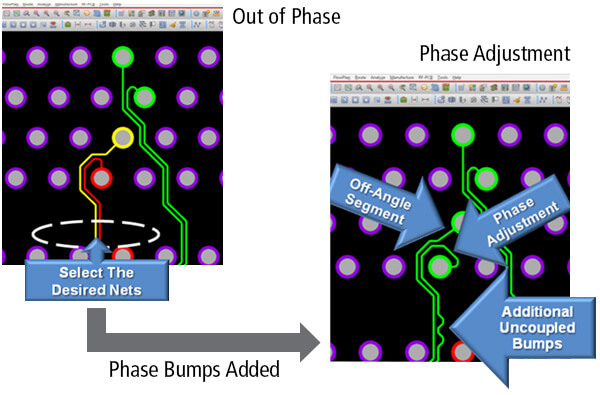

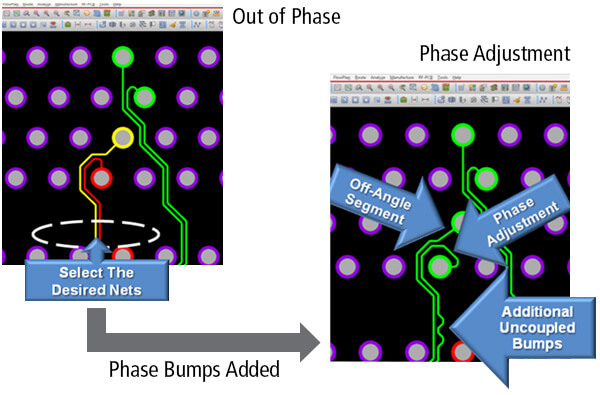

AiPT

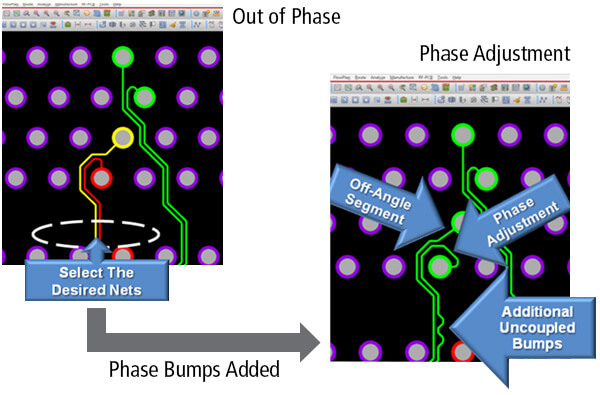

Auto-interactive Phase Tuning (AiPT) automatically matches dynamic and static phases for the selected differential pairs. It works with a set of parameters that provides you with several options for trace lengthening or shortening as well as pad entry/exit options. With AiPT, you can significantly shorten the time to match static and dynamic phases for differential pairs

Key Benefits

- Innovative environment with smart target technology

- Accelerates timing closure by 4X

- Solves timing closure challenge

Cadence® Allegro® TimingVision™ technology provides an innovative and unique environment that allows you to see real-time delay and phase information right on the routing canvas.

As data rates increase and supply voltages decrease in today’s high-performance interfaces (i.e. DDR3/DDR4, PCle® Gen3 and SATA), PCB and IC package designers have to spend more time to ensure that signals in an interface meet timing requirements. With increasing density, the effort to get to timing closure—ensuring all signals meet timing requirements—can increase significantly. Layout designers need new tools to meet this increasingly complex challenge.

With the embedded route engine, the Allegro TimingVision environment provides real-time feedback during interactive editing and enhances your ability to develop a strategy for resolving timing on large buses or interfaces such as DDRx and PCIe. Coupled with Auto-interactive Phase Tuning (AiPT) and Auto-interactive Delay Tuning (AiDT) capabilities, this environment lets you speed timing closure of high-speed PCB interfaces by up to 75%.

AiDT

Auto-interactive Delay Tuning (AiDT) automatically generates tuning patterns on a user-selected routed byte lane or interface based on user-defined timing constraints and tuning parameters. AiDT computes the required length for the connections to meet timing constraints, and utilizes controlled push/shove techniques when adding tuning patterns.

Key Benefits

- Innovative environment with smart target technology

- Accelerates timing closure by 4X

- Solves timing closure challenge

Cadence® Allegro® TimingVision™ technology provides an innovative and unique environment that allows you to see real-time delay and phase information right on the routing canvas.

As data rates increase and supply voltages decrease in today’s high-performance interfaces (i.e. DDR3/DDR4, PCle® Gen3 and SATA), PCB and IC package designers have to spend more time to ensure that signals in an interface meet timing requirements. With increasing density, the effort to get to timing closure—ensuring all signals meet timing requirements—can increase significantly. Layout designers need new tools to meet this increasingly complex challenge.

With the embedded route engine, the Allegro TimingVision environment provides real-time feedback during interactive editing and enhances your ability to develop a strategy for resolving timing on large buses or interfaces such as DDRx and PCIe. Coupled with Auto-interactive Phase Tuning (AiPT) and Auto-interactive Delay Tuning (AiDT) capabilities, this environment lets you speed timing closure of high-speed PCB interfaces by up to 75%.

AiDT

Auto-interactive Delay Tuning (AiDT) automatically generates tuning patterns on a user-selected routed byte lane or interface based on user-defined timing constraints and tuning parameters. AiDT computes the required length for the connections to meet timing constraints, and utilizes controlled push/shove techniques when adding tuning patterns.

AiPT

Auto-interactive Phase Tuning (AiPT) automatically matches dynamic and static phases for the selected differential pairs. It works with a set of parameters that provides you with several options for trace lengthening or shortening as well as pad entry/exit options. With AiPT, you can significantly shorten the time to match static and dynamic phases for differential pairs

以下内容为机器自动翻译,可能存在翻译不准确的情况

主要好处

- 智能目标技术的创新环境

- 加快4倍的定时关闭

- 解决时间关闭挑战

Cadence® Allegro® TimingVisionTM技术提供了一个创新和独特的环境,允许您直接在路由画布上查看实时延迟和相位信息。

随着当今高性能接口(即DDR3/DDR4、PCle® Gen3和SATA)、PCB和IC软件包设计者必须花更多时间确保接口中的信号满足定时要求。随着密度的增加,达到定时关闭的努力——确保所有信号满足定时要求——可以显著增加。布局设计师需要新的工具来应对这一日益复杂的挑战。

借助嵌入式路由引擎,Allegro TimeingVision环境在交互式编辑期间提供实时反馈,并增强了您在DDRx和PCIe等大型总线上制定解决计时策略的能力。再加上自动交互相位调优(AiPT)和自动交互延迟调优(AiDT)功能,此环境允许您将高速PCB接口的定时关闭速度提高高达75%。

AiDT

Auto-interactive Delay Tuning (AiDT) automatically generates tuning patterns on a user-selected routed byte lane or interface based on user-defined timing constraints and tuning parameters. AiDT computes the required length for the connections to meet timing constraints, and utilizes controlled push/shove techniques when adding tuning patterns.

AiDT

自动交互延迟调优(AiDT)根据用户定义的定时约束和调优参数,在用户选择的路由字节车道或接口上自动生成调优模式。AiDT计算连接满足定时约束所需的长度,并在添加调优模式时使用受控推/推技术。

AiPT

自动交互相位调优(AiPT)会自动匹配所选差分对的动态和静态相位。它适用于一组参数,这些参数为您提供了几个跟踪加长或缩短选项以及垫片进出选项。使用AiPT,您可以显著缩短差分对的静态和动态相位匹配时间