核心优势

- 用于单芯片和多芯片引线键合,倒装芯片和晶圆级芯片封装,硅中介层,芯片堆叠以及其他高级封装技术的完整的从前端到后端的物理设计全流程

- 基于芯片/封装级优化的有效及芯片级IP保护的分布式协同设计

- 约束驱动的基板互连设计,提取,建模和信号完整性分析

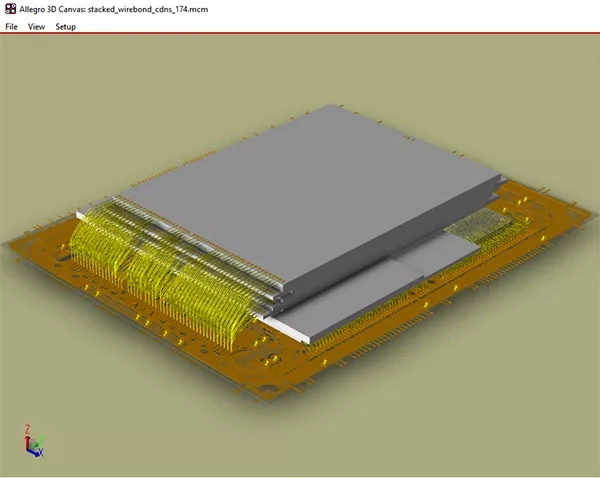

Cadence® Allegro® Package Designer Plus能够实现约束驱动的设计校正的封装基板布局。它支持用于单芯片和多芯片BGA / LGA封装设计的完整的从前端到后端的物理实现流程。提供了一组针对特定封装特性的强大功能,例如动态库开发,连接生成/优化,多层引线键合,协同设计,管芯堆叠和TSV,嵌入式腔体,推式布线,报告和量产输出。

系统设计集成

Allegro Package Designer Plus与Cadence OrbitIO™系统规划全集成,可提供完整的封装物理设计功能,以帮助您更早地,更有信心地进行战略权衡。 该工具还提供与Cadence Sigrity™,Clarity™和Celsius™分析技术的直接接口,提供集成的布局和分析流程,几乎支持所有先进的IC封装技术,例如复杂的引线键合,铜柱,FOWLP,2.5D,3D ,BGA和PoP。

主要功能

- 具有实时校正的数据库,物理设计规则和电气约束的实时DRC的单芯片和多芯片封装的优化物理布局解决方案

- 约束驱动的“一推一推”交互式布线,自动交互和全自动布线

- 提供复杂的设计规则和电气约束驱动布局

- 灵活的模型连接,支持网表,原理图和“实时”连接

- 包括核心DesignTrue DFM规则检查法

- 可视化并执行3D引线和设计规则检查

技术文档

技术博客 I PCB的DDR4布线指南和PCB的架构改进

计算机领域总是在持续不断地进步,始终有发展变化和更新迭代等待着我们去体验和探索。从头开始打造一台新的 PC 是一种令人愉悦的体验,有新一代标准时更是如此。说到这里,我们不得不提到有关随机存取存储器 (…

兼顾接口的设计方法

加快 PCB 原理设计和实现的层次化方法 Key Benefits 将原理设计和实现速度提高 15%以更高的抽象水平设计 PCB更快地针对基于标准的接口进行布线,包括 DDR3、DDR4、SATA 和…

约束驱动电源完整性核签,确保满足电源分配网络(PDN)的限制,更快完成设计并减少签发压力

在更短的时间内完成检查、调试、返工和组装 PCB,借助增强现实(AR)技术减少错误

联系我们

满天星是 Cadence授权代理商,为您提供专业技术服务。有关 Cadence软件的销售、试用、技术支持或培训,请联系我们。